Vrije Universiteit Amsterdam

Universiteit van Amsterdam

Master Thesis

## A Reo Semantics for Reasoning about Speculative Execution

| Author:         | Hans-Dieter A. Hiep      | (2526195) |

|-----------------|--------------------------|-----------|

| 1st supervisor: | dr. Jasmin C. Blanchette | (VU)      |

| cosupervisor:   | prof. dr. Farhad Arbab   | (CWI)     |

| 2nd reader:     | dr. Femke van Raamsdonk  | (VU)      |

A thesis submitted in fulfillment of the requirements for the joint UvA-VU Master of Science degree in Computer Science

October, 2018

#### Abstract

Speculative execution is a technique used in popular processors designed in the past decade, e.g. by Intel and AMD. Take, for example, this imperative program:

```

int outcome = slowOperation();

if (outcome < 0) doThis();

else doThat();</pre>

```

Before the slowOperation() is finished executing, one may speculate on its outcome. There is a *branch prediction function* that chooses a value, which we call a *speculation*, used to evaluate the **if**-statement concurrently with the slowOperation(). The outcome can be negative or non-negative, leading to the speculative execution of doThis() or doThat(), respectively. Once the slowOperation() returns, its actual outcome is known. If the speculation is incorrect when compared with the actual outcome, then we need to undo any of the computational steps performed based on such a *false speculation*. This ensures that no unwanted steps are visible outside the processor. Otherwise, if the speculation is correct, then we have gained throughput by already performing steps ahead of time based on a *true speculation*.

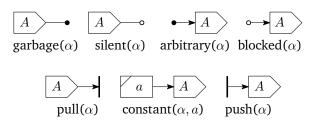

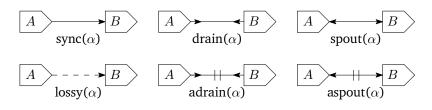

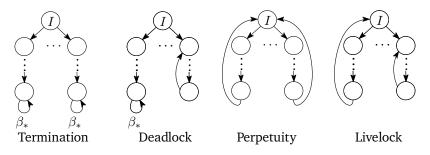

Reo is a language for compositional construction of protocols for the coordination of concurrent and distributed systems. As far as we know, Reo has never before been used to study speculative executions. We design a typed language of compositions and components inspired by Reo. We introduce components not modeled before in Reo: PROPHET and PULL. PROPHET is a component that generate speculations. PULL is a component that enforces progress and forbids deadlocks. The behavior of components are constrained using formulas in a firstorder logic with data types and data streams. This logic is expressive enough to formulate properties such as *deadlock-freedom* and *livelock-freedom*, and other properties important for understanding speculative executions in concurrent and distributed systems: *delay insentivity, independence, (a)synchronicity, termination, instantaneousness, linearity* and *causality*.

# Contents

| 1   | Intr  | oduction 1             |

|-----|-------|------------------------|

|     | 1.1   | Speculative Execution  |

|     | 1.2   | Running Example        |

| 2   | Lang  | guage 13               |

|     | 2.1   | Compositions           |

|     | 2.2   | Interfaces             |

|     | 2.3   | Components             |

| 3   | Fou   | ndation 23             |

|     | 3.1   | Data Streams           |

|     | 3.2   | Logical Formalism      |

|     | 3.3   | Coordination Protocols |

|     | 3.4   | Coordination Games     |

| 4   | Com   | aponents 35            |

|     | 4.1   | Endpoints              |

|     | 4.2   | Channels               |

|     | 4.3   | Buffers                |

|     | 4.4   | Nodes                  |

| 5   | Prop  | perties 45             |

|     | 5.1   | Independence           |

|     | 5.2   | Synchronicity          |

|     | 5.3   | Deadlock and Livelock  |

|     | 5.4   | Instantaneousness 57   |

|     | 5.5   | Linearity              |

|     | 5.6   | Causality              |

| 6   | Con   | clusion 63             |

|     | 6.1   | Summary                |

|     | 6.2   | Related Work           |

| Bil | oliog | raphy 65               |

## Acknowledgments

Many thanks to Farhad Arbab for inspiring discussions, suggesting interesting research topics, and reading thoroughly through this thesis while providing lots of comments on this document. Thank you, Jasmin Blanchette, for the many discussions how to write effectively, for providing useful feedback, and giving the right definition of the logical formalism.

Thank you a lot, Benjamin Lion, for sharing an office, always willing to listen to ideas, and having many deep discussions on concurrency, Reo, Kleene, Russels, and Spinoza. Thanks for the oportunities for discussion and insightful comments given by Kasper Dokter and Sung-Shik Jongmans.

Other people that deserve thanks: Femke van Raamsdonk (for being the second reader of this document), Jacco van Splunter & Roy Overbeek (for discussion), and Wan Fokkink (for his inspiring teaching).

Special thanks go to the people of the Centrum voor Wiskunde & Informatica (CWI) for allowing work on this thesis during an internship period of fourty-five weeks. In particular, thank you, Steven Pemberton, for giving a good reason to come to CWI, and Frank de Boer for approving the internship. Thanks to Jana Wagemaker, Keyvan Azadbakht, Vlad Serbanescu, Jan Rutten, and others in the Formal Methods group for being nice collegues.

To those other people not listed here, but who still provided useful support: thank you!

This page is intentionally left blank.

### Chapter 1

# Introduction

A recent interest in the security of microcode architectures of mainstream processors revealed issues (popularly known as Meltdown, Spectre, and Foreshadow; see Kocher et al. [54]). These architectural issues demonstrate side-channel attacks caused by a combination of branch prediction, cache hierarchy, simultaneous multi-threading and speculative execution. In particular, it turns out that when computation is not reversible under certain conditions, this leads to a systematic leakage of privileged information. Mitigation of these issues has serious impact for large-scale computing service providers: under certain workloads perceived performance is reduced by 50% [4].

Speculative execution is a well known technique that allows for the optimization of concurrent systems. Over the course of the critical path of an execution, the number of idle resources varies. One may exploit idle resources by speculative execution that potentially shortens the critical path length to increase throughput. However, speculative execution may also negatively affect throughput if a false speculation must be reverted.

The essence of reversible computing is that every operation can be reverted. This has beneficial properties in itself: ideally, a reversible computation does not dissipate power and thus is highly energy efficient [77]. Some claim that adoption of reversible computing is necessary [40]: the rate of performance improvements of general-purpose computing, as seen in the last decades, comes at greater energy cost than before. Reversible computing allows for significantly less energy usage without negatively affecting performance, thus allowing for performance improvements to continue.

In this thesis, we aim to gain an intuitive understanding of concurrency, speculative execution, and reversible computing. Our vision is to establish logical foundations for concurrent and distributed systems. We employ a structured approach by modeling interactive computing systems as coordination protocols using Reo. Reo is a coordination language for compositional construction of interaction protocols [9, 8]. Coordination is the study of dynamic topologies of interaction between computing systems [5].

On the practical side, Reo manifests as a high-level declerative programming language for constructing concurrent and distributed systems. For example, recently developed compilers produce concurrency glue code which links together single-threaded code. Programmers write single-threaded code in a supported programming language, and design interaction patterns in Reo: the compiler fills in the gap. This is beneficial to programmers who no longer need to have in-depth technical knowledge of concurrency, likely leading to an increase in productivity and decrease in the number of concurrency-related software bugs.

There are two benefits of raising the level of abstraction that programmers use to define interactions. First, abstraction alleviates programmers from directly working with low-level concurrency primitives (e.g. semaphores, locks, send/receive) and debugging concurrency errors (e.g. race conditions, deadlocks). Instead, programmers specify coordination protocols decleratively, to define the permissible interactions among external single-threaded programs, thus separating their concerns for computation and concurrency. Second, experiments show that concurrency code generated by Reo compilers has run-time performance similar to hand-crafted concurrency code [49]. This is achieved by performing program optimization directly on the higher-level coordination protocols, as opposed to the lower-level of concurrency primitives.

Over the years Reo has developed a rich theory, as demonstrated by over thirty formal semantics [50]. These semantics can be roughly divided into three groups: co-algebraic models (e.g. streams), operational models (e.g. automata), and others. We introduce yet another semantics of Reo, and use it to explore fundamental properties of concurrent and distributed systems. Properties related to speculative execution are more easily expressed in our semantics than in other Reo semantics.

Our presentation of Reo is novel in a way: we focus on the detection of inconsistencies. An inconsistency is a situation in which no valid behavior is specified. Such inconsistencies are effectively resolved by tracing back to a nearest branch point from which execution can be resumed safely. We shed light on dualities present in our language, by the definition of so-called BUFFERS and PROPHETS, that correspond to history variables and future variables [1]. Our language is a dialect of Reo. We define a calculus of graphical notations for components. We have designed a type checker that is closely related to classical sequent calculus [29, 34].

The main result of this thesis is the establishment of a logical formalism for defining specifications of the behavior of components, and properties important for understanding speculative execution. We define the syntax of our typed coordination language (Chapter 2). We use a first-order logic for expressing primitive component as formulas, and compositionally interpret our coordination language as *coordination protocols* (Chapter 3). Coordination games are introduced in Section 3.4. We provide a non-exhaustive overview of components (Chapter 4). We establish the properties of *delay insensitivity, independence, synchronicity* and *asynchronicity, progress* and *termination, deadlock-freedom* and *livelockfreedom, instantaneousness, linearity,* and *causality* (Chapter 5). We finally argue that this thesis is a contribution to the logical foundations of concurrent and distributed systems, and the logical foundations of Reo in particular (Chapter 6).

### **1.1 Speculative Execution**

Central processing units (CPUs) with an instruction pipeline architecture employ out-of-order execution as a technique to increase performance of single-threaded code [76]. The behavior of a single-threaded program is defined by the order of its instructions. With out-of-order execution, instructions can execute aheadof-time such that the overall system behavior is correspondingly equivalent to that of an in-order execution. Reordering instructions in a pipeline increases the throughput of executed instructions, by efficiently planning the use of computational resources such as arithmetic and logic units (ALUs) and floating point units (FPUs), that results in better run-time performance.

At the level of CPUs, speculative execution is a variant of out-of-order execution. A *speculation* predicts a future state of a processor, and consequent instructions are performed ahead-of-time under the assumption of validity of that future state. At some time after a prediction, actual processor state is compared with the earlier predicted state. If the predicted future state is valid, then the processor has performed a *true speculation* and the consequent instructions correspond to that of an in-order execution. However, if the predicted future state is not valid, then the effects of instructions performed under a *false speculation* need to be reverted.

Speculative execution does not apply to hardware only. For example, speculative multi-threading implements speculative execution in software [18]. Speculative execution is also conceivable in distributed systems.<sup>1</sup>

Speculative execution in concurrent systems can either increase or decrease throughput [44]. The rate of increased throughput depends on the particular implementation technique applied, of which there are multiple. We consider a simplistic model of the two extreme cases: embarrassingly parallel and backtracking.

An *embarrassingly parallel* implementation branches into multiple isolated systems and performs computation in all branches concurrently. The separate branches are isolated systems and thus may not communicate with each other. The number of branches is the size of the domain of the prediction, e.g., a Boolean prediction branches off into two systems. Precisely one branch assumes the true speculation. This technique has the highest gain in throughput because every possibility executes concurrently. Branches that compute based on a false speculation are simply discarded.

A *backtracking* implementation chooses a single branch at a time, as in our previous example of CPUs. We require a branch prediction function, that is typically chosen to maximize the likelihood of a true speculation. The branch prediction function determines which branch to perform first. If this branch is based on a false speculation, the branch is discarded by reverting computation back to the point where the true speculation branches off. This technique requires computation in a branch to be reversible, to be able to revert in the case of a false speculation. Throughput may be affected negatively if one takes a branch assuming a false speculation, since the branch first needs to be reverted before the true computation may commence. Thus, the quality of the branch prediction function greatly impacts the cost of a backtracking implementation.

In summary, we think of these two extremes as a trade-off between time and space. The *embarrassingly parallel* implementation has negligible time overhead, but has a space overhead linear in the number of branches to compute speculatively. The *backtracking* implementation has negligible space overhead, but requires time linear in the depth of the speculative computation that needs to be reverted. Other techniques exists between these extremes: for example, *ea*-

<sup>&</sup>lt;sup>1</sup>It is an urban legend that sending a specific HTTP responses before any HTTP request is received increases throughput of web-servers. This was supposedly used in early webcam software [63].

ger execution executes all branches with negligible space overhead by preemptive scheduling, similar to an iterative deepening search strategy [79].

Throughout this section, we construct a (toy) processing unit to explain speculative execution in more detail. Our toy is used as the running example. The construction of a processing unit is not necessarily centralized (like CPUs), and can also be considered a decentralized processing unit. It is not our goal to construct a fully functional CPU. Our approach is as follows:

- 1. We construct our processor in a modular fashion to allow reasoning about smaller individual pieces first. Compositionality of reasoning ensures that the end result of composing all pieces together behaves as designed. This explains the basics of how to use Reo to compose components.

- 2. We give a high-level and low-level explanation of how components communicate and cooperate. This gives us a better intuition for understanding the formal theory, and helps us understand the nature of speculative execution.

The intended purpose of our example is to demonstrate three layers:

- 1. Syntax. The functionality of our processor is specified by combining specifications of more primitive components. Our syntax makes this combination explicit and unambiguous.

- 2. Semantics. Components interact by means of playing a coordination game. The objective of the game is to avoid any inconsistent configurations.

- Logic. We reason about compositional properties, and the necessity of reversibility of computations based on speculation, to argue that backtracking is an effective implementation strategy.

### **1.2 Running Example**

Essential units in processors are arithmetic units. It is well known that arithmetical operations, such as addition, multiplication, and division, are not always constant-time operations: complexity of these operations depens on trade-offs made by processor architects.

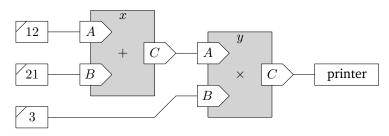

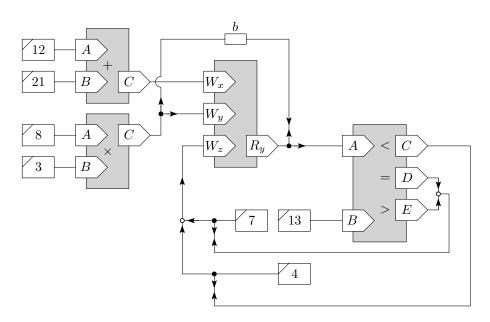

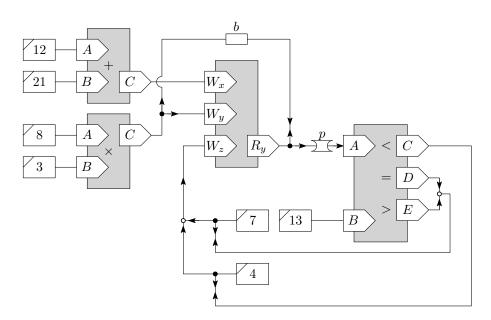

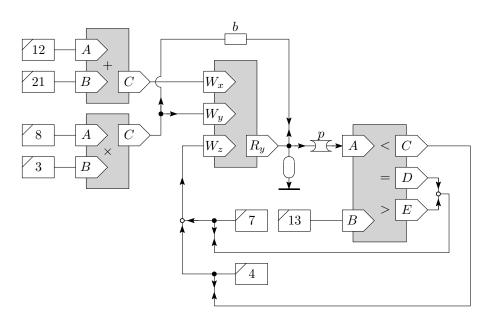

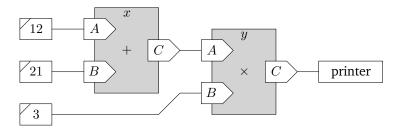

Suppose we wish to compute  $(12+21) \times 3$ . We consider the following two functional components: ADDITION and MULTIPLICATION. The following circuit combines these components, and connects the input to the values 12, 21, 3 and the output to some printing device.

The ADDITION component simultaneously takes the values 12 and 21 and computes their sum. The MULTIPLICATION component takes this result and the value 3 and multiplies them. Finally, the result of 99 is printed.

A component consists of ports to allow for external information flow, or *interaction* with the outside world. These ports form the interface of a component. An input port allows external information to flow in, and an output port allows information to flow out.

This circuit forms a *composition* of two components. There are two instances: x and y. The first is an instance of an ADDITION component, the latter an instance of a MULTIPLICATION component. Each instance of a component has a number of ports, which we write qualified as x.A, x.B, x.C, y.A, y.B, y.C. In our composition, we link ports together to indicate that these ports are identical: here x.C and y.A are linked together to mean that the output port C of x is the input port A of y. We call this *identification*.

The white boxes around our composition are part of an experimental setup: the values 12, 21, 3 are ready for consumption and the printer is ready to accept an outcome. These are not part of the composition, and instead form a testing environment. Ports *x*.*A*, *x*.*B*, *y*.*B*, *y*.*C* are linked to the testing environment.

If we were to observe the data that flows through ports during experimentation we can collect a trace. The arithmetical components are functional, meaning that they only operate if all of their inputs are available. The component asynchronously computes its output at some later time. Typically, one abstracts this fact by assuming that arithmetic is performed instantaneously, but in our example we use arithmetic to demonstrate speculative execution.

Other essential units are logical units that can compare values and perform logical operations. The outcome of a logical operation allows so-called branching, where we test a condition and conditionally perform operations.

Consider, for example, comparing 12 with 13. If they are equal, we print some value; otherwise, we do nothing. In a typical imperative programming language, e.g. pseudo Java, one would write:

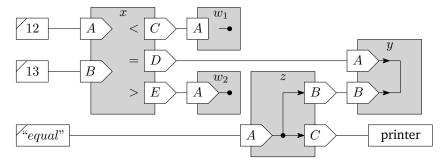

This is given declaratively by the following circuit:

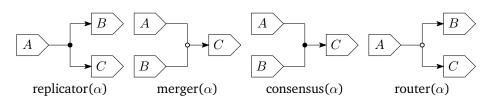

There are five components in this picture, again surrounded by a testing environment. The component x is a comparator that compares x.A and x.B. We have two instances of the same component:  $w_1$  and  $w_2$  are both a so-called GARBAGE component that disposes all its inputs. The component y is a SYNCHRONOUS DRAIN that mediates synchronization in this circuit. Component z is a REPLICATOR that instantaneously transports its input z.A by duplicating it to z.B and z.C.

The semantics of this circuit is as follows: if *x*.*A* is smaller than *x*.*B*, then *x*.*C* fires a signal; if *x*.*A* equals *x*.*B*, then *x*.*D* fires; if *x*.*A* is larger than *x*.*B*, then *x*.*E*

fires. The REPLICATOR and SYNCHRONOUS DRAIN act as a CONTROL VALVE. If x.D fires a signal, only then the SYNCHRONOUS DRAIN allows an input on y.B. However, if x.D does not fire, then y.B is inhibited. This inhibition spreads through the REPLICATOR, blocking its input z.A. Thus, in case the two inputs are equal, we have that y synchronizes this result with the REPLICATOR, allowing it to output to z.C into the printer.

In the imperative program, the conditional check is typically assumed to be performed causally before the print statement. In our circuit, the conditional check and the output to the printer are synchronous: they happen instantaneously to the observer. This means that, in principle, the output can be sent to the printer before the conditional check is performed. Intuitively, synchronous actions express atomic groupings of actions, which represents an abstraction of the precise ordering of individual actions, as this ordering is irrelevant.

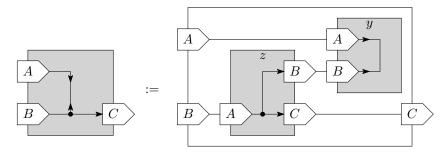

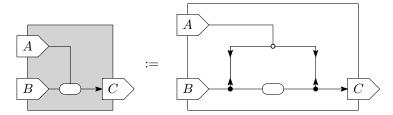

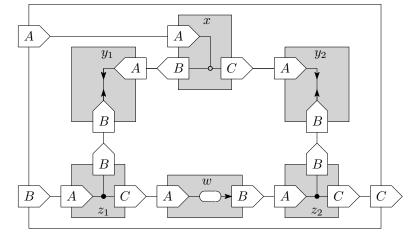

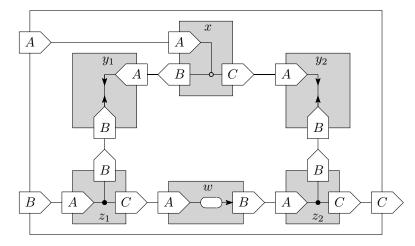

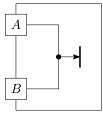

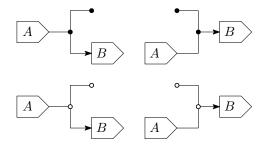

That the REPLICATOR and SYNCHRONOUS DRAIN act as a CONTROL VALVE can be made explicit, by turning it into a composite component:

The left-hand side of := is the graphical mnemonic that defines the composite component on the right-hand side of :=. The composite component is defined by a composition of the primitive components y and z. Primitive here means that we no longer decompose such component any further. Our composite component has three ports on its boundary: A, B, C. We make explicit which port we mean, by qualifying the ports by its instance. The ports at the boundary of the defined composite component remain unqualified. Here we link A to y.A and B to z.A. Internally, we link z.B to y.B. The output of z.C is linked to C.

Whenever we use the composite component, A and B act as input ports that accept values. We may link only output ports to input ports. From the interior perspective, A and B act as input ports. However, at the exterior of y and z, these ports A and B are output ports of the surrounding composition. The direction of a boundary port in the interior is opposite to the exterior. For example, from the perspective of the interior of our composition and the exterior of y, we link the input port A to the output port y. However, the port y. A acts as an input port from the interior perspective of y.

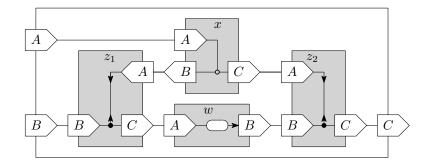

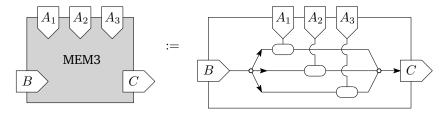

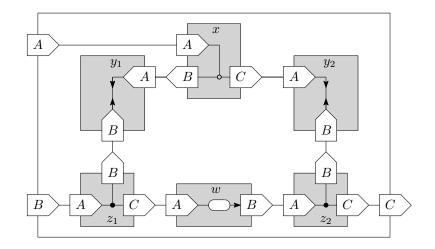

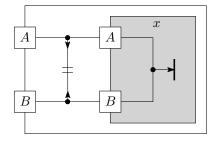

Another essential unit in processors are registers and memory banks. Typically, memory in modern CPUs is layed out in a cache hierarchy. This means that accessing memory has variable and dynamic latency. We specify a simple memory bank by first considering memory cells. Memory cells are modeled using CONTROLLED VARIABLES, for which we reuse our earlier defined CONTROL VALVE:

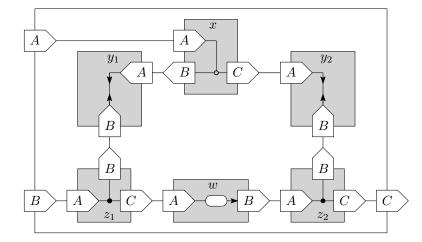

Our composition consists of two CONTROL VALVES ( $z_1$  and  $z_2$ ), a ROUTER (x), and a VARIABLE (w). Port A controls one of the two valves on B and C, with a VARIABLE in between. In this picture all input and output ports are explicitly denoted. This quickly clutters the view.

In this picture we no longer draw the component boundaries.

The so-called VARIABLE is a primitive component which we consider in Example **??**. For now, think of VARIABLES as a component that continuously outputs its most recently supplied input value, if any. Thus a VARIABLE may output its value multiple times. Reading of an empty VARIABLE is blocked. VARIABLES may be overwritten. The CONTROLLED VARIABLE only accepts input or supplies output if port *A* fires. Due to the ROUTER of signal *A*, our CONTROLLED VARIABLE does not accept input and supply output at the same time. It is impossible for all ports to fire simultaneously: *B* or *C* fire only if *A* fires.

A VARIABLE is not reversible because we can overwrite a value without it ever being read: consider that it is possible to overwrite a previously stored value by supplying a value to *B* twice in a row. The write cannot be reverted, since the previous value is lost in the process of overwriting. Since a VARIABLE is not reversible, so is a CONTROLLED VARIABLE: the presence of *A*, the ROUTER, and CONTROL VALVES does not prevent the possibility of overwriting.

A memory bank consists of multiple memory cells, and a single memory cell can be activated using an address. The address encodes which memory cell is active. We consider a memory bank of three memory cells:

To read from this memory bank, we supply an address to A and observe the output port C. To write, we supply an address to A and supply a value to B.

The memory bank consists of these components: a demultiplexer, that takes an address value (e.g. 1,2,3) and translates it into a signal (e.g.  $A_1, A_2, A_3$ ). We have three CONTROLLED VARIABLES that model three memory cells, connected to these signals: a ROUTER takes the input at *B* and is connected to the input of each cell. A MERGER takes the output of each cell and merges into the output *C*. Both are depicted with a white dot, but the reader can infer from the direction of the arrow which component is a ROUTER and which is a MERGER.

We assume that the initial value of all memory cells is empty. An empty memory cell cannot be read, meaning that its output port does not fire. For a non-empty memory cell, reading it produces its current value as output.

Now consider the following pseudo-Java code, that assigns to three VARI-ABLES:

| x = 12 + 21;  | $W_x$ |

|---------------|-------|

| y = 8 * 3;    | $W_y$ |

| if (y < 13) { | $R_y$ |

| z = 4;        | $W_z$ |

| } else {      |       |

| z = 7;        | $W_z$ |

| }             |       |

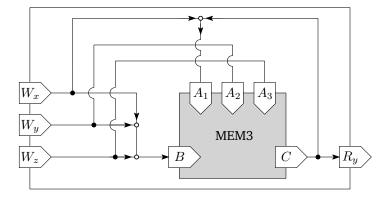

We have the following memory actions:  $W_x$ ,  $W_y$ ,  $W_z$  for write actions, and  $R_y$  for a read action. Each action happens only once in our snippet. We take that x, y, z are stored in memory cells 1,2,3. The addresses are encoded by constants. We create the following components:

These memory actions are connected to the arithmetical and logical units:

This circuit demonstrates the intended out-of-order behavior of our processor. The + and × components may independently compute their results. Suppose that 12 + 21 was finished computing after  $8 \times 3$ , then  $W_y$  happens before  $W_x$ . Since  $R_y$  must happen after  $W_y$ , we have inserted a BUFFER component (named x in the diagram). The BUFFER adds a causal dependency. After reading  $R_y$  and comparing it with 13, we either assign 7 or 4 to z: all these actions happen after  $W_y$ . It is still possible in our circuit that  $W_x$  is delayed, after  $W_z$ .

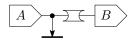

A BUFFER is a component. For now, it intuitively behaves as follows. It waits for an input to arrive, and stores it in its single-place memory. While the BUFFER is full, no new input may arrive. After some time, it may release its output and clears its memory.

In our circuit, the BUFFER *b* stores the computed value of *y*, but this value is not significant: only the memory value that is output by  $R_y$  is being compared. In this circuit these two values are identical. However, in a more complicated example where memory can also be affected by other components, the expected behavior would be to compare the memory value.

The BUFFER is closely related to another component, which we call a PROPHET. A PROPHET generates a speculation, and stores that speculation in its memory. It then waits for the arrival of the true value. If that value equals the speculation the PROPHET reset its speculated memory, similar to a BUFFER that outputs a value, and them becomes empty. If the arrived value is different than the speculation, then it means we had done a false speculation. A PROPHET blocks its input port from firing with the true value, typically resulting in a deadlock.

Consider inserting a PROPHET p between the REPLICATOR after  $R_y$  and before A of the comparator, as shown in the following circuit:

The intended behavior of this circuit is now different: we speculate on the value of *y* in our program, before we actually know the value of  $R_y$ . Suppose that y < 13: then  $W_z$  fires with 4. Suppose that  $y \ge 13$ : then  $W_z$  fires with 7. Both actions could occur before  $W_y$ .

If  $y \ge 13$  was speculated, and some time later the actual value is read from memory and  $R_y$  fires (here with 21), then we have a true speculation. Thus, we have already performed computation (writing 7 to *z*), thereby gaining throughput. Moreover, if y < 13 was speculated, and some time later the actual value is read (again 21), then we have a false speculation. Thus, we must discard or revert our computation, thereby losing throughput.

However, there is no guarantee that the value actually be read from memory: the PROPHET allows blocking its input port indefinitely if the speculation differs from the true value. We must enforce that eventually a flow from  $R_y$  to the input of the PROPHET takes place, otherwise the components deadlock in the case of a false speculation. We modify our circuit to add the constraint of progress, that forces an inconsistency in case of a false speculation:

The forcing component, called PULL, acts as a suction pipe: adding this component forbids, by specification, that these components enter a deadlock configuration. However, addition of only a PULL means that  $R_y$  and A always keep firing, which is too strict. Thus, we additionally add a variable in between the REPLICATOR and the PULL, to indicate that  $R_y$  must fire *at least once*.

We explore this example in more depth by deconstructing each component and understanding them individually. For that, we first require a language that allows us to express compositions, interfaces and components. This page is intentionally left blank.

### Chapter 2

## Language

We define a formal language for the construction of components. The formal language works on three levels:

- 1. Compositions describe how individual components are wired together. We refer to individuals by instance variables and their ports.

- 2. Interfaces describe the types and the names of boundary ports. We define how to check the interface of a composition.

- 3. Components comprise layers of compositions of composites and primitives. We have components bound to instance variables, we show how to simplify components by substitution by flattening the layers, and how to check whether a component is well-typed.

Our language is graphical, and was used in the earlier running example. This work on syntax based on Reo is similar in purpose to Dokter's textual Reo [33], in which he allows user-defined component types. The crucial difference is the explicit treatment of nodes in this work, whereas Dokter implicitly uses merger-replicators nodes. Furthermore, we describe a mechanism for type checking compositions and components, and simplification of components.

The theory described in this chapter was developed alongside a prototype Java program that parses, normalizes and type checks compositions and components. The developed prototype is not included with this thesis, since it likely is incorrect, and incomplete, and thus not of high quality.

The design of the type system for checking components and compositions is based on the  $\overline{\lambda}\mu\mu$ -calculus by Curien and Herbelin [29]. The notion of duality of components and swapping input and output ports, is based on the work by Downen and Ariola [34].

#### 2.1 Compositions

We first introduce compositions and how to link components together. We consider well-formedness of compositions and typed compositions. The motivation for doing so is to structure our understanding of composition, and thus allow us to do structural reasoning on compositions.

Let there be a set of *data types*. Data types are denoted  $\alpha$ , $\beta$ ,..., instance variables are denoted *x*,*y*,*z*,..., and port variables are denoted *X*,*Y*,*Z*,...

Definition 1. A reference is as given by the following grammar:

$$p,q,r,s := x X^{\alpha} \mid X^{\alpha}$$

where *x* is an instance variable, *X* is a port variable, and  $\alpha$  a type annotation. The type annotation  $\alpha$  may be omitted if unambiguous or clear from context.

Let *R* denote the set of references. References are either *qualified* (x.X) or *unqualified* (X). Intuitively, references allow us to point to a port: if we point to a port of an instance, then it is a qualified reference; if we point to a boundary port of a composite component, then it is an unqualified reference.

Definition 2. A *composition* is as given by the following grammar:

$$c,d,e ::= x \mid (c \parallel d) \mid (c)_a^p$$

where *x* is an instance variable,  $(c \parallel d)$  a *parallel composition*, and  $(c)_q^p$  an *identification*, such that the following laws hold:

$$(c || c) = c$$

$$(c || d) = (d || c)$$

$$(c || (d || e)) = ((c || d) || e)$$

$$((c)_q^p)_q^p = (c)_q^p$$

$$((c)_q^p)_s^r = ((c)_s^r)_q^p$$

$$((c)_q^p || d) = ((c || d))_q^p$$

That is, parallel composition is idempotent, commutative, and associative; identification is idempotent, commutative, and distributes over parallel composition.

A composition is an instance variable, a parallel composition of two compositions, or an *identification* of two references and a composition. The top reference of an identification is called the *source*, and the bottom reference is called the *sink*. Identification  $(c)_q^p$  respects sources and sinks, that is  $(c)_q^p \neq (c)_p^q$ . We have the notion of *occurrence* of instance variables (being atomic compositions) and references (of identifications).

It should be noted that a source or a sink is an output or an input, depending on ones perspective. Whenever a component is used, then its interface is flipped (its inputs become outputs, or equivalently, its sources become sinks) allowing one to connect a source to a sink.

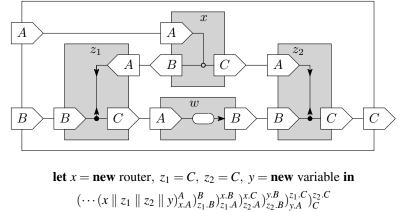

**Example 3.** In the above figure we have the following references: *x*.*A*, *x*.*B*, *x*.*C* for the ROUTER, *y*<sub>1</sub>.*A*, *y*<sub>1</sub>.*B* and *y*<sub>2</sub>.*A*, *y*<sub>2</sub>.*B* for the SYNCHRONOUS DRAINS, *z*<sub>1</sub>.*A*, *z*<sub>1</sub>.*B*, *z*<sub>1</sub>.*C*, and *z*<sub>2</sub>.*A*, *z*<sub>2</sub>.*B*, *z*<sub>2</sub>.*C* for the REPLICATORS, and *w*<sub>1</sub>.*A*, *w*<sub>1</sub>.*B* for the VARIABLE: types are omitted. The inner part of the composition is:  $(x || y_1 || y_2 || z_1 || z_2 || w)$  formed out of all components without their identifications. Since parallel composition is associative we do not write parentheses. The composition with all identifications is:

$$(\cdots (x || y_1 || y_2 || z_1 || z_2 || w)^A_{x,A})^{x,B}_{y_1,A})^{x,C}_{y_2,A})^B_{z_1,A})^{z_1,B}_{y_1,B})^{z_1,C}_{w,A})^{w,B}_{z_2,A})^{z_2,B}_{y_2,B})^{z_2,C}_C$$

A composition can be simplified into a normal form. First, we push out all identifications by distributivity to obtain a composition in which all parallel compositions are deep, and identifications are on the surface. Next, we associate all nested parallel compositions to the right to form a list of instances. Next, we sort the instances according to some order of instance variables, removing duplicates. The surface identifications also form a list of pairs of references. We sort this list according to the lexicographic orders of pairs of references, removing duplicates. The result has the shape  $(\cdots(((x \parallel (\ldots \parallel z)))_q^p) \cdots)_s^r$  such that instances are ordered, and references are lexicographically ordered. All compositions have a unique normal form.

We typically work with compositions that are in normal form. We call the *inner part* of a composition to be the parallel composition of instance variables  $(x \parallel (... \parallel z))$ , and the *outer part* consists of all surrounding identifications.

A composition denotes a finite set of instance variables and a finite relation of references. The set of instance variables of a composition precisely occur in that composition, and similar for references. More precisely, *x* is represented by the set {*x*} and the empty relation,  $(c \parallel d)$  is represented by the union of the sets and relations of the representations of *c* and *d*, and  $(c)_q^p$  is represented by adding (p,q) to the relation of the representation of *c*. For example,  $(((x)_{x,Y}^{y,Z} \parallel y)_{x,Z}^{y,X}$  is represented by {*x*,*y*} and {(y.Z, x.Y), (y.X, x.Z)}, and so its normal form is  $((x \parallel y)_{x,Z}^{y,X})_{x,Y}^{y,Z}$ .

We want to prevent certain compositions: forbidding the identification of ports of unknown instances, forbidding identifying references more than once, and forbidding references to occur as both source and sink. This ensures that every reference resolves to an instance that occurs in the composition, and that identification is in some sense affine: a port is never referenced more than once.

**Definition 4.** A composition is *well-formed* if:

- every reference qualified by an instance has that instance occur in the composition,

- every reference is used at most once.

The last condition implies that a reference is used exclusively as a source or a sink, and that a reference is not identified with itself. A well-formed composition is easily recognized by looking at its normal form. The first condition is checked by verifying that each qualified reference's instance occurs in the sorted list of instances deeper in the composition. The last condition is checked by verifying that a reference never occurs twice in a row in either normal form.

An example of well-formed compositions is:  $(x)_Y^{x,X}$  denotes the composition of instance variable *x* of which its external port *x*.*X* is identified with the internal port *Y* at the boundary of our composition.

Here are some negative examples.  $(y)_X^{X,Y}$  is not well-formed because *x* does not occur.  $((y)_X^{y,Y})_Z^{y,Y}$  is not well-formed because *y*.*Y* occurs twice.  $(y)_X^X$  and  $((y)_Y^X)_X^Z$  are not well-formed because *X* is both a source and sink.

A well-formed composition is verified by ensuring that every qualified reference has an instance that is contained in the set of instance variables, and that the relation is a partial function (each element is related to at most one other), injective (each related element is mapped to by a unique element), irreflexive (no element is related to itself), and acyclic (no element is transitively related to itself).

### 2.2 Interfaces

We still want to prevent more compositions: compositions must only identify ports of the same type, and we want to keep track of the interface of a component to resolve references against. Towards this, we first introduce interfaces.

**Definition 5.** An *interface* is a pair of two disjoint sets of references, denoted  $\langle p_1, \ldots, p_n | q_1, \ldots, q_k \rangle$ . An *unqualified interface* is an interface consisting only of unqualified references. A *qualified interface* is an interface consisting only of qualified references.

The empty interface is denoted as  $\langle | \rangle$ . We define the following operations on interfaces. Let  $X_1, \ldots, X_n$  and  $Z_1, \ldots, Z_k$  be port variables. Given an unqualified interface  $U = \langle X_1, \ldots, X_n | Z_1, \ldots, Z_k \rangle$ , we may *qualify* it by an instance *x*, denoted *x*.*U*, to mean the qualified interface  $\langle x.X_1, \ldots, x.X_n | x.Z_1, \ldots, x.Z_k \rangle$ . By  $U^{\perp}$  we denote the dual interface:  $U^{\perp} = \langle Z_1, \ldots, Z_k | X_1, \ldots, X_n \rangle$ . The variables on the lefthand side of the | in an interface are called *input* port variables and those on the right-hand side are called *output* port variables. The dual of an interface swaps input and output. We may implicitly coerce interfaces to a set of references, being the union of the two disjoint sets of references the interface comprises.

We may also lift union to interfaces. Let  $\Delta_1, \Delta_2, \Theta_1, \Theta_2$  be sets of references. Given two interfaces  $U = \langle \Delta_1 | \Theta_1 \rangle$  and  $V = \langle \Delta_2 | \Theta_2 \rangle$ , by  $U \cup V$  we mean the interface obtained by pairwise union of the two parts of the interfaces to form  $\langle \Delta_1 \cup \Delta_2 | \Theta_1 \cup \Theta_2 \rangle$ .

Now we introduce typed compositions. Consider the typing judgment x :: U of an instance variable x and unqualified interface U. A *typed compositions* c : U is a well-formed composition c and an interface U. Let a typing context be a set of typing judgments  $\Gamma$ . We define the relation  $\vdash$  between typing contexts and typed compositions, as given by Figure 2.1.

Since atomic compositions are always fully qualified, the union of interfaces never has overlapping names. As a side-condition to these rules, we assume that for  $p,\Delta$  it holds that  $p \notin \Delta$ , and for  $\Theta, q$  it holds that  $q \notin \Theta$ . We have not written type annotations in compositions for brevity: they are the same as the annotation given in the interface.

Given a well-formed composition c. If there exists a typing context  $\Gamma$  and interface U such that  $\Gamma \vdash c : U$ , then we say that c is a *well-typed composition*. The intention of a well-typed composition is to ensure that references are used

| $\overline{\Gamma, x :: U \vdash x : x.U}  \overline{\Gamma}$ | $\frac{\Gamma \vdash c : \langle \Delta \mid \Theta \rangle}{\vdash (c)_Y^X : \langle X^{\alpha}, \Delta \mid \Theta, Y^{\alpha} \rangle}$                 | $\frac{\Gamma \vdash c : \langle x. X^{\boldsymbol{\alpha}}, \Delta \mid \boldsymbol{\Theta}, y. Y^{\boldsymbol{\alpha}} \rangle}{\Gamma \vdash (c)_{y.Y}^{x.X} : \langle \Delta \mid \boldsymbol{\Theta} \rangle}$ |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                               | $\frac{\Gamma \vdash c : \langle \Delta \mid \Theta, y. Y^{\alpha} \rangle}{\Gamma \vdash (c)_{y.Y}^{X} : \langle X^{\alpha}, \Delta \mid \Theta \rangle}$ | $\frac{\Gamma \vdash c : \langle x. X^{\alpha}, \Delta \mid \Theta \rangle}{\Gamma \vdash (c)_Y^{x.X} : \langle \Delta \mid \Theta, Y^{\alpha} \rangle}$                                                            |

Figure 2.1: Typing rules for compositions.

linearly and that identification of two references are of the same type. We assume that all compositions we work with in the sequel are well-typed (and thus well-formed), unless stated otherwise.

**Example 6.** In the above figure, the interface of the ROUTER is  $\langle B, C | A \rangle$ , that of the SYNCHRONOUS DRAIN is  $\langle | A, B \rangle$ , that of the REPLICATOR is  $\langle B, C | A \rangle$  and that of the VARIABLE is  $\langle B | A \rangle$ . These interfaces are flipped because we have used these components in a composition. In the composition  $(x || y_1)$ , we refer to *x* and  $y_1$  and thus take the qualified interfaces for *x* and  $y_1$ :  $\langle x.B, x.C | x.A \rangle$  and  $\langle | y_1.A, y_1.B \rangle$ , which composed are:  $\langle x.B, x.C | x.A, y_1.A, y_1.B \rangle$ . We can then identify the output *x*.*B* and input  $y_1.A$ , resulting in  $\langle x.C | x.A, y_1.A \rangle$ . The rest of the composition is then formed. Ultimately, we end up with  $\langle A | B, C \rangle$  as interface for the composition with all identifications.

#### 2.3 Components

Next, we consider the construction of components. Our intention is that a component is either a primitive component, or a composite component consisting of primitive components. To do so, we consider the construction of components as either a well-typed composition, or a binding of an instance variable to a primitive component. We assume a given set of primitive components, where each primitive component is denoted by name.

**Definition 7.** A *component* is as given by the following grammar:

$$C, D, E ::= c \mid \text{new } R \mid (\text{let } x = C \text{ in } D)$$

where c is a well-typed composition (see Definition 4), **new** R is a primitive component R, and **let** binds the instance variable x in D. We consider composite components equal modulo renaming of bound instance variables.

Certain components contain redundancies. We simplify components according to the following three rules, that rewrites the pattern on the left-hand side of  $\rightarrow$  to the right-hand side. The first rule removes bindings for non-occurring instances:

$$(\mathbf{let} \ x = C \ \mathbf{in} \ D) \quad \longrightarrow \quad D \tag{2.1}$$

with the side-condition that x does not occur in D, hence x is unused and the binding can be eliminated. The second rule permutes bindings:

$$(\mathbf{let} \ x = (\mathbf{let} \ y = C \ \mathbf{in} \ D) \ \mathbf{in} \ E) \quad \longrightarrow \quad (\mathbf{let} \ y = C \ \mathbf{in} \ (\mathbf{let} \ x = D \ \mathbf{in} \ E)) \tag{2.2}$$

with the side-condition that y does not occur in E, or if it does it is suitably renamed: the nested **let** binding is pulled back to the outer level. The third rule substitutes compositions:

$$(\mathbf{let} \ x = c \ \mathbf{in} \ C) \quad \longrightarrow \quad C[x.c/x][x] \tag{2.3}$$

A substitution C[c/x] denotes standard substitution of each occurrence of an instance variable x by the composition c. A composition c is qualified with instance variable x, which is denoted x.c, by substituting every occurring unqualified reference X by x.X. A non-well-formed composition c is *linked through* the instance variable x, by finding identifications with sink p and source x.X and sink x.X and source q for each port X, removing these two identifications, and identifying pand q in the resulting composition if  $p \neq q$ . We denote linking through of a nonwell-formed composition c as c[x]. Linking through is lifted to components C[x]by replacing each occurring composition c by c[x].

Qualification and linking through preserves well-formed composition: given a well-formed composition *c* bound to *x*, and given a well-formed composition *d*, then the composition d[x.c/x][x] is well-formed. Clearly, substituting an instance variable by a qualified composition makes a non-well-formed composition, as in the example qualifying  $(y)_B^A$  with *x* results in  $(y)_{x,B}^{x,A}$  and its substitution of *y* in  $(x)_{x,A}^{x,B}$  results in the non-well-formed composition  $((y)_{x,A}^{x,B})_{x,B}^{x,A}$ . By linking through, we obtain  $(y)_{x,B}^{x,B}$  or  $(y)_{x,A}^{x,A}$ , both of which link through to *y*.

Lemma 8. Component rewriting using these rules terminates.

*Proof.* We measure the number **let** bindings and the depth of left nested bindings, and in all rules either one decreases.  $\Box$

**Example 9.** Take the term let  $x = ((y)_A^{y,X})_{y,Y}^B$  in  $((x)_Z^{x,A})_{x,B}^W$ . We assume *y* is a component with interface  $\langle X | Y \rangle$ . What follows is that within the composition of *x*, we link *y*.*X* and *y*.*Y* to the unqualified references *A* and *B*, where *A* is a sink and *B* is a source. We qualify every unqualified reference by its instance variable, substitute the composition for each occurrence of the bound instance variable, and then resolve the identifications by linking them through. The first step results in the qualification of references:  $((y)_A^{y,X})_{y,Y}^B$  becomes  $((y)_{x,A}^{y,X})_{y,Y}^{x,B}$ . The second step results in  $((((y)_{x,A}^{y,X})_{y,Y}^{x,B})_{x,B}^{x,A})_{x,B}^W$  where *x* is replaced by  $((y)_{x,A}^{y,X})_{y,Y}^{x,B}$ .

| $\Gamma \vdash c : U  U$ is unqualified |                              | $\Gamma \vdash C :: V  \Delta, x :: V^{\perp} \vdash D :: U$ |

|-----------------------------------------|------------------------------|--------------------------------------------------------------|

| $\Gamma \vdash c :: U$                  | $\vdash$ <b>new</b> $R :: U$ | $\Gamma, \Delta \vdash $ let $x = C$ in $D :: U$             |

Figure 2.2: Typing rules for composite components.

last step removes identifications by linking through: we link *y*.*X* to *Z* via *x*.*A* and remove *x*.*A* to obtain  $(((y)_{y,Y}^{x,B})_{Z}^{y,X})_{x,B}^{W}$ , and we link *y*.*Y* to *W* via *x*.*B* and remove *x*.*B* to obtain  $((y)_{Z}^{y,X})_{y,Y}^{W}$ .

Once no simplification rule applies anymore, we obtain components in normal form. These components are either of the form of a primitive component, **new** *R* for some primitive *R*, or a composite component, **let**  $x = \text{new} R_1$  in  $(...(\text{let } z = \text{new} R_n \text{ in } c)...)$ , with zero or more bindings to primitives  $R_1$  up to  $R_n$ . The latter is also written as **let**  $x = \text{new} R_1, ..., z = \text{new} R_n$  in *c*.

#### Lemma 10. Every component has a unique normal form.

*Proof.* We apply the critical pair method to establish confluence. By confluence and termination, we have unique normal forms. There are five critical pairs:

- 1. Rules 2.1 and 2.3: (let x = c in D) either discards x because it does not occur in D, or substitutes and links through. If x does not occur in D, we have D[x.c/x] = D and D[x] = D since substitution without occurrence leaves the term untouched, and linking through without occurrence leaves the term untouched for well-formed compositions.

- 2. Rules 2.2 and 2.2: (let x = (let y = (let z = C in D) in E) in F) is joined to (let z = C in (let y = D in (let z = E in F)))

- 3. Rules 2.1 and 2.2: (let x = (let y = C in D) in E) reduces in one step to E if x does not occur in E, or in three steps if both x and y do not occur in E.

- 4. Rules 2.2 and 2.1: (let x = (let y = C in D) in E) reduces in one step to (let x = D in E) if y does not occur in D, or in two steps if y does not occur in D and E.

- 5. Rules 2.2 and 2.3: (let x = (let y = c in D) in E) reduces in one step to (let x = D[y.c/y][y] in E) and in two steps to the same term, since y is not contained in E the same argument as for the first case applies that restricts the effects of substitution and linking through only to the D subterm.

We now consider typing judgments and typing contexts of components. Let U, V be unqualified interfaces, and C :: U a typing judgment, and let the typing context  $\Gamma$  denote a set of typing judgments. We define a relation between typing contexts and a single typing judgment of a composite component, denoted  $\Gamma \vdash C :: U$ , as given by Figure 2.2. We consider the rules from left to right:

1. Recall that the difference between *c* :: *U* and *c* : *U* is that the former judges only unqualified interfaces, whereas the latter judges arbitrary interfaces. Hence, for a composition to become a composite component, it is required to have an unqualified interface. This is possible by identifying all qualified references.

- 2. This is a family of rules, one rule for each primitive component R with unqualified interface U. We admit this rule for each primitive component together with U as its unqualified interface.

- 3. This rule shows that *x* can be bound in *D*. This dualizes the interface of *C* and binds it to *x* in the context of component *D*: what we used to consider an output for C, now is an input to D; and what we used to consider an input to C, now is an output for D. By  $\Gamma, \Delta$  we mean that  $\Gamma$  and  $\Delta$  are disjoint: this ensures that an instance can be used in only a single composition.

A component *C* such that  $\emptyset \vdash C$  is derivable is called a *closed component*.

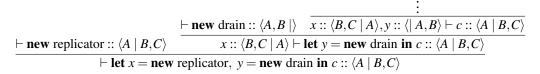

Example 11. We now take a component from before and show how it is normalized. The first things to fix are the primitive components, of router ::  $\langle A \mid B, C \rangle$ , valve ::  $\langle A \mid B, C \rangle$  and variable ::  $\langle A \mid B \rangle$ . The component valve is formed by composing replicator ::  $\langle A | B, C \rangle$  and drain ::  $\langle A, B | \rangle$  as:

let x = new replicator, y = new drain in  $((((x \parallel y)_{y,A}^A)_{y,B}^B)_{y,B}^{x,B})_C^{x,B})$

this forms the following derivation:

where *c* is our composition  $((((x || y)_{y,A}^A)_{x,A}^B)_{y,B}^{x,B})_C^{x,C}$  that can be checked to be well-typed with the unqualified interface  $\langle A | B, C \rangle$ . Let *C* denote this closed component. We can form the component of the controlled memory by reusing our earlier component, as follows:

After normalization and renaming we obtain the component shown below:

let x = new router,  $y_1 =$  new drain,  $z_1 =$  new replicator,  $y_2 =$  new drain,  $z_2 =$  new replicator, w = new variable in  $(\cdots (w || x || y_1 || y_2 || z_1 || z_2)^A_{x,A})^B_{z_1,A})^{w,B}_{y_2,A})^{x,C}_{y_1,B})^{z_1,C}_{y_1,B})^{z_2,B}_{w,A})^{z_2,C}_{y_2,B})^{z_2,C}_{C}$

This page is intentionally left blank.

### Chapter 3

## Foundation

We consider the formulation of constraints over time to specify the behavior of components. These formulas are called *coordination protocols*. Every primitive component is specified by its interface and its coordination protocol. Of a composite component, we inductively construct its coordination protocol from the structure of composition and the coordination protocols of its underlying primitives.

To do so formally, in this chapter we describe a particular many-sorted logic and its standard interpretations as data constraints on streams. This is useful, since we can not only use the logical formalism to define the behavior of primitive components, but also properties of components.

- 1. We first lay down the mathematical preliminaries required in the rest of this chapter: the domains of data types and streams.

- 2. We define our many-sorted logic and introduce standard interpretations. Satisfiability can be understood as finding sets of assignments of ports to streams.

- 3. We specify the behavior of primitive components by coordination protocols. We consequently lift component specifications for composite components by induction on their construction.

- 4. We define coordination games as the interaction between environment and component.

Our loigcal formalism is inspired by Dokter's formal rule-based semantics [32]. He defines coordination protocols as relations of data streams. He defines a modal logic equiped with stream constraints that are constructed using stream head equality, stream derivatives, and modal operators. In our formalization, we employ standard first-order logic to define coordination protocols. It seems that this change does not result in the loss of any expressiveness.

#### 3.1 Data Streams

Data types are algebraic structures. Streams are used to model the flow of data. By  $\mathbb{N}$  we denote the set of *natural numbers* 0,1,2,3,...

Let a *data type* be a structure (D, \*) where *D* is a carrier set and  $* \in D$  is a designated constant. We speak of *data elements* as those elements in *D* different from \*. Whenever we speak of *elements* or *values*, we mean data elements or \*.

Intuitively, one may think of \* as standing for the absence of data, being a 'null' value. We assume equality of data types is decidable. We write  $\alpha, \beta, \ldots$  to denote data types. As convention, we write  $a \in \alpha$  to mean some element *a* of the carrier set. The set  $\mathbb{N}$  is a data type ( $\mathbb{N}$ ,0) where we take \* = 0.

Let a stream be a function from natural numbers to some set. We denote streams by the Greek letters  $\sigma, \tau, \ldots$ . Intuitively, one thinks of streams as an enumeration. *Data streams* are functions from naturals to data types, e.g.  $\sigma$ :  $\mathbb{N} \rightarrow \alpha$  for some data type  $\alpha$ . Alternatively, we may define streams by stream differential equation. See [71, 70] for an elementary introduction.

A stream differential equation for some stream  $\sigma$  is given by its initial value  $\sigma(0)$  and its stream derivative  $\sigma'$ . The derivative itself is also a stream such that  $\sigma'(x) = \sigma(x+1)$ . We have the repeated derivatives  $\sigma''$ ,  $\sigma'''$ , and so on: we define  $\sigma^{(0)} = \sigma$  and  $\sigma^{(n+1)} = (\sigma^{(n)})'$ . We have that  $\sigma(n) = \sigma^{(n)}(0)$ . From an initial value and stream derivative we construct the stream  $(\sigma(0), \sigma(1), \sigma(2), ...)$ .

For example, let Nat = { $\mathbb{N}$ ,\*} be some data type where \* = 0. The enumeration (0,0,0,...), that repeats 0 forever is a stream. Given directly as a function,  $\sigma(x) = 0$  defines this stream. Given as a stream differential equation,  $\sigma(0) = 0$  and  $\sigma' = \sigma$  also defines this stream.

There are more streams than natural numbers. The argument is a variation of Cantor's diagonalization argument that there exists more real numbers than natural numbers. There are at least as many streams as there are natural numbers: let n a natural number, then we can construct the stream (n, \*, ...), where the first element is n, followed by \* repeated forever.

Suppose towards contradiction that there are as many natural numbers as there are streams. We enumerate all streams in a table: let  $\sigma_0$  denote the first stream,  $\sigma_1$  the second stream, and so on. Look at the diagonal and construct a stream  $\tau$  such that  $\tau(x) = \sigma_x(x) + 1$ . Stream  $\tau$  differs from each enumerated stream  $\sigma_x$  in at least one position, *x*. Thus it cannot be part of the enumeration. This contradicts that there are as many natural numbers as streams.

Equality of streams is established by bisimilarity [15]. A relation *R* on two streams is called a (stream) bisimulation if for all  $(\sigma, \tau) \in R$ ,

$$\sigma(0) = \tau(0)$$

and  $(\sigma', \tau') \in R$ .

Two streams  $\sigma$ ,  $\tau$  are bisimilar if there exists a bisimulation relation R such that  $(\sigma, \tau) \in R$ , and we write  $\sigma = \tau$ .

#### 3.2 Logical Formalism

We now consider a many-sorted first-order logic with equality. The general structure of this section follows much from [35]:

- 1. We define syntax: what we mean by signature, terms, and formulas.

- 2. We define semantics: what we mean by standard interpretation.

- 3. We define the notions of assignment, solution, satisfiability and validity.

What is different than usual is our treatment of streams, and quantification over streams. The intention of our logical formalism is to be able to use tools such as interactive theorem provers (e.g. Coq, Isabelle, or Lean) to implement our semantics. Further implementation within these tools is out of the scope of this thesis. We first start with the definition of signatures. Signatures may contain more non-logical symbols than those given here: we specify only the minimal requirements. This treatment conveys openness and extensibility of our formalism.

**Definition 12.**  $\Sigma = (S, F, P)$  is a *signature* consisting of the following data:

- *S* is a set of *sorts*, such that:

- for each data type  $\alpha$  there is a distinct sort  $\alpha \in S$ ,

- for each data type  $\alpha$  there is a distinct sort  $(\mathbb{N} \to \alpha) \in S$ .

- *F* is a set of *function symbols*, such that:

- for each data type  $\alpha$ ,  $*_{\alpha} \in F$  with arity  $\langle \alpha \rangle$ ,

- for each data value  $d \in \alpha$ ,  $d_{\alpha} \in F$  with arity  $\langle \alpha \rangle$ ,

- $+ \in F$ ,  $\in F$ ,  $\times \in F$  with arities  $\langle \mathbb{N} \rangle$ ,  $\langle \mathbb{N}, \mathbb{N} \rangle$ , and  $\langle \mathbb{N}, \mathbb{N}, \mathbb{N} \rangle$ ,

- for each data type  $\alpha$ , at<sub> $\alpha$ </sub>  $\in$  *F* with arity  $\langle (\mathbb{N} \rightarrow \alpha), \mathbb{N}, \alpha \rangle$ ,

- for each data type  $\alpha$ , skip $_{\alpha} \in F$  with arity  $\langle (\mathbb{N} \to \alpha), \mathbb{N}, (\mathbb{N} \to \alpha) \rangle$ .

- *P* is a set of *predicate symbols*, such that:

- $\bot, \top \in P$  with arity  $\langle \rangle$ ,

- for each data type  $\alpha$ ,  $=_{\alpha} \in P$  with arity  $\langle \alpha, \alpha \rangle$ ,

- $\leq \in P$  with arity  $\langle \mathbb{N}, \mathbb{N} \rangle$ .

An *arity* is a list of sorts  $(s_1, ..., s_n)$  where  $s_1, ..., s_n \in S$ . Each function symbol has an associated non-empty arity. Each predicate symbol has an associated arity.

Since  $\mathbb{N}$  is a data type, we also have a distinct sort  $\mathbb{N} \in S$ . Any natural number  $0, 1, 2, 3, \ldots$  can be taken as a constant. We now fix some signature  $\Sigma = (S, F, P)$ . The definitions for terms and formulas are not surprising. Each term is assigned to a sort. We define terms inductively over all sorts simultaneously. Formulas are also defined inductively.

**Definition 13.** Let  $s \in S$  be a sort. A *term of sort* s is formed by:

- a variable *x* of sort *s* is an atomic term of sort *s* denoted *x<sup>s</sup>*,

- if  $c \in F$  is a function symbol of arity  $\langle s \rangle$ , then c is an atomic term of sort s,

- if  $t_1, \ldots, t_n$  are terms of sorts  $s_1, \ldots, s_n$  and  $f \in F$  is a function symbol of arity  $\langle s_1, \ldots, s_n, s_{n+1} \rangle$ , then  $f(t_1, \ldots, t_n)$  is a term of sort  $s_{n+1}$ .

**Definition 14.** A *first-order formula* is:

- if  $p \in P$  is a predicate symbol of arity  $\langle \rangle$ , then *p* is an atomic formula,

- if  $t_1, \ldots, t_n$  are terms of sort  $s_1, \ldots, s_n$  and  $p \in P$  is a predicate symbol of arity  $\langle s_1, \ldots, s_n \rangle$ , then  $p(t_1, \ldots, t_n)$  is an atomic formula,

- non-atomic formulas are formed with connectives  $\neg$ ,  $\land$ ,  $\lor$ ,  $\rightarrow$ ,

- non-atomic formulas are formed by quantifiers  $\exists x^s, \forall x^s$ .

We define *standard interpretations* to fix the interpretation of the non-logical symbols we have introduced in our signature.

**Definition 15.** A standard interpretation  $\mathcal{M}$  of signature  $\Sigma = (S, F, P)$  consists of:

- a map of sorts to domain such that  $s \in S$  maps to domain  $s^{\mathcal{M}}$ , such that:

- $\alpha^{\mathcal{M}}$  is the carrier set of data type  $\alpha$ ,

- the sort  $(\mathbb{N} \to \alpha) \in S$  is mapped to data streams  $\mathbb{N} \to \alpha$  of data type  $\alpha$ .

- a map of function symbols to domain functions such that  $f \in F$  with arity  $\langle s_1, \ldots, s_n, s_{n+1} \rangle$  maps to a function  $f^{\mathcal{M}} : s_1^{\mathcal{M}} \times \cdots \times s_n^{\mathcal{M}} \to s_{n+1}^{\mathcal{M}}$ , and  $c \in F$  with arity  $\langle s \rangle$  maps to  $s^{\mathcal{M}}$ , such that:

$- *^{\mathcal{M}}_{\alpha}$  is the null value  $* \in \alpha$ ,

- $d_{\alpha}^{\mathcal{M}}$  is the data value  $d \in \alpha$ ,

- $-+, -, \times$  are interpreted as the arithmetical functions of plus, monus<sup>1</sup> and times,

- $at_{\alpha}$  is interpreted as a function  $at_{\alpha}^{\mathcal{M}} : (\mathbb{N} \to \alpha) \times \mathbb{N} \to \alpha$  such that at<sup> $\mathcal{M}$ </sup><sub> $\alpha$ </sub>( $\sigma$ )(n) =  $\sigma$ (n),

- $\operatorname{skip}_{\alpha}^{\mathcal{M}}$  is interpreted as a function  $\operatorname{skip}_{\alpha}^{\mathcal{M}} : (\mathbb{N} \to \alpha) \times \mathbb{N} \to (\mathbb{N} \to \alpha)$  such that  $\operatorname{skip}_{\alpha}^{\mathcal{M}}(\sigma)(n) = \sigma^{(n)}$ .

- a map of predicate symbols to domain relations such that  $p \in P$  with arity  $\langle s_1, \ldots, s_n \rangle$  maps to a relation  $p^{\mathcal{M}} : s_1^{\mathcal{M}} \times \cdots \times s_n^{\mathcal{M}}$ , and  $p \in P$  with arity  $\langle \rangle$ maps to propositions, such that:

- $\perp^{\mathcal{M}}$  never holds and  $\top^{\mathcal{M}}$  always holds,  $=_{\alpha}^{\mathcal{M}}$  is equality of values of data type  $\alpha$ ,  $\leq^{\mathcal{M}}$  is the relation of less than or equals between naturals.

Let  $\mathcal{M}$  denote a fixed standard interpretation. Towards defining satisfiability and validity, we define the notion of assignment. This is necessary, since not every domain element has a corresponding term.

**Definition 16.** An assignment  $\beta$  is a map from variables to domain elements, where variables  $x^s$  are mapped to elements in  $s^{\mathcal{M}}$ .

Given the interpretation of function symbols in  $\mathcal{M}$ , an assignment can be extended to a map from terms to domain elements, defined inductively on the structure of terms. Similarly, given the interpretation of predicate symbols in  $\mathcal{M}$ , an assignment can be extended to a map from formulas to propositions, defined inductively on the structure of formulas, making use of the previously extended assignment to a map from terms to domain elements.

The *satisfiability* of a formula  $\phi$  is denoted  $\beta \models \phi$  and is defined to be equivalent to the truth of  $\phi$  interpreted as a proposition given assignment  $\beta$ . The *validity* of a formula  $\phi$  is denoted  $\models \phi$  and holds if and only if  $\beta \models \phi$  holds for all assignments  $\beta$ .

**Proposition 17.** If  $\beta_1, \beta_2$  are two assignments and  $\beta_1(x^s) = \beta_2(x^s)$  for all free variables  $x^s$  in  $\phi$ , then  $\beta_1 \models \phi$  and  $\beta_2 \models \phi$ .

An assignment that is restricted to map only the free variables of a formula  $\phi$  is called a *solution* for  $\phi$ . We have a special class of formulas:

**Definition 18.** A *coordination protocol* is a first-order formula  $\phi$ , where all free variables  $x^s$  of  $\phi$  must be of sort  $s = (\mathbb{N} \to \alpha)$  for some  $\alpha$ . These free variables are also called the *ports* (of data type  $\alpha$ ) of  $\phi$ .

Remark 19. We treat sort annotations implicitly, to prevent clutter. We also use a more convenient notation for  $\operatorname{at}_{\alpha}$  and  $\operatorname{skip}_{\alpha}$ : let *X* be a port of sort  $(\mathbb{N} \to \alpha)$ and t be a variable of sort N, then the term  $at_{\alpha}(X,t)$  is written as X(t) and the term skip<sub> $\alpha$ </sub>(X,t) is written as X<sup>(t)</sup>. We call such terms applications and derivations, respectively. Additionally, we use t > s for  $\neg(t \le s)$ , and s < t for t > s, and s = tfor  $s \leq t \wedge t \leq s$ .

<sup>&</sup>lt;sup>1</sup>Monus is minus for natural numbers by rounding negative numbers to 0.

### 3.3 Coordination Protocols

We employ coordination protocols to encode our intuition of the behavior of components. Formally, coordination protocols are formulas as defined in last section. The set of solutions of a coordination protocol is a set of tables of observations. It was found that this idea has an origin in Kleene's 1951 paper on representation of events [53]. Informally, observations represent a consistent snapshot of the data flowing through ports of a component, made by an independent observer. Tables of such observations capture behavior of a component over time. A set of tables of observations corresponds to accepting certain such behaviors and rejecting others.

**Definition 20.** The coordination protocol  $\phi$  induces a set  $\mathcal{L}(\phi) = \{\beta \mid \beta \vDash \phi\}$  of solutions of  $\phi$ .

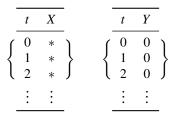

A coordination protocol  $\phi$  is called inconsistent it  $\mathcal{L}(\phi)$  is empty. Intuitively, we consider the set  $\mathcal{L}(\phi)$  of solutions as a set of tables of observations. Consider these examples:

**Example 21.** Let *X* and *Y* be ports of type Signal = {\*,0}. The coordination protocols  $\forall t.X(t) = *$  and  $\forall t.Y(t) = 0$  have one free variable: *X* and *Y*, respectively. The sets of tables of observations are shown below. Both contain single solution.

Another example is the coordination protocol  $\forall t.X(t) = * \lor Y(t) = *$  that has two free variables: *X* and *Y*. Its set of tables of observations is shown below. This set contains any solution  $X \mapsto \sigma, Y \mapsto \tau$  where  $\sigma$  and  $\tau$  are data streams such that  $\sigma(t) = *$  or  $\tau(t) = *$  for any  $t \in \mathbb{N}$ .

| _ | t | X | Y  | t | X | Y |          | t | X | Y |    | t | X | Y   |

|---|---|---|----|---|---|---|----------|---|---|---|----|---|---|-----|

| ( | 0 | * | *  | 0 | 0 | * |          | 0 | * | 0 |    | 0 | 0 | *   |

| ļ | 1 | * | *, | 1 | * | * | <i>,</i> | 1 | 0 | * | ,, | 1 | * | 0 , |

|   |   |   |    |   |   |   |          |   |   |   |    |   |   |     |

|   | ÷ | ÷ | ÷  | ÷ | ÷ | ÷ |          | : | ÷ | ÷ |    | ÷ | ÷ | :   |

Consider two coordination protocols  $\phi$  and  $\psi$  that do not have any free variables in common. The protocol  $\mathcal{L}(\phi)$  consists only of solutions of  $\phi$ , and similar for  $\mathcal{L}(\psi)$  and solutions of  $\psi$ . The intersection of these two sets is empty, however  $\mathcal{L}(\phi \land \psi)$  is not empty. In  $\mathcal{L}(\phi \land \psi)$ , every solution in  $\mathcal{L}(\phi)$  is paired with every solution in  $\mathcal{L}(\psi)$  and glued together.

**Example 22.** The solutions of  $\forall t.X(t) = *$  and  $\forall t.Y(t) = 0$  can be glued together to form the coordination protocol:

| X Y Z                                 | X Y Z               | X Y Z                                                                 |

|---------------------------------------|---------------------|-----------------------------------------------------------------------|

| $\begin{pmatrix} d & d \end{pmatrix}$ | $(\bar{e} \bar{e})$ | $\overline{(\underline{d} \ \underline{d})} \overline{\underline{d}}$ |

Figure 3.1: Intersection of frame conditions.

| X M Z                                                                                       | X M Z                                                              | X M Z                    |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|

| $\boxed{\begin{array}{c} \hline \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | $\overbrace{\begin{smallmatrix} * & d \\ d \end{smallmatrix}}^{*}$ | $\overline{(* d d)}_{*}$ |

Figure 3.2: Three frame conditions that make up a BUFFER.

$$\left\{\begin{array}{cccc}

t & X & Y \\

0 & * & 0 \\

1 & * & 0 \\

2 & * & 0 \\

\vdots & \vdots & \vdots

\end{array}\right\}$$

We illustrate our intuition using frame conditions.

**Example 23.** The frame conditions X(0) = Y(0) and Y(0) = Z(0). This condition applies to only the first row. These two frame conditions are overlapped, they restrict the allowed observations in the first element, as in Figure 3.1. The first constraint allows any value to appear at *Z* in the first row. The second constraint allows any value to appear at *X* at the first row. But the constraints combined only allow elements that are equal to all *X*, *Y*, and *Z*. These constraints, however, do not restrict any other value at other ports.

If we want a frame condition to persists over time, then it must constrain every row. The intuition of universal quantification is to *slide* the frame condition over all rows.

**Example 24.** In Figure 3.1, the first frame condition then is X(t) = Y(t) and we universally quantify over time t, to obtain  $\forall t.X(t) = Y(t)$ . The second has as frame condition Y(t) = Z(t), and universally quantified it becomes  $\forall t.Y(t) = Z(t)$ . Hence, the first coordination protocol only has solutions for which at every time X and Y have the same value; it does not restrict Z in any way. Similar for the second coordination protocol. Conjunction of the two protocols,  $(\forall t.X(t) = Y(t)) \land (\forall t.Y(t) = Z(t))$ , results in the constraint that all three ports, at all times, must have the same value.

**Example 25.** A frame condition that spans multiple rows is the example in Figure 3.2. The condition ranges over two rows. The first frame condition specifies that: if port X has some value d and M has no value and Z has no value, then d must be in the next row of M. The intuition here is that M acts as a sort of memory, that is updated by constraining its value in the next row. The second frame condition specifies that memory is retained whenever there is no input or output. The third frame condition specifies that the contents of memory is the same as at port Z

Figure 3.3: Example sequence of solutions, with constraints of a BUFFER.

and that the memory is cleared in the next row. We now obtain the coordination protocol:

$$\forall t. ( Z(t) = * \land M(t) = * \land M(t+1) = X(t) \lor$$

$$X(t) = * \land Z(t) = * \land M(t) \neq * \land M(t+1) = M(t) \lor$$

$$X(t) = * \land Z(t) = M(t) \land M(t) \neq * \land M(t+1) = *)$$

We have the quantifier  $\forall t$ . on the outer level to ensure that for each row, one of these three frame conditions applies. If we would take  $(\forall t...) \lor (\forall t...) \lor (\forall t...)$  as coordination protocol, then we accept streams that have for all rows, either only the first, only the second, or only the third frame condition, and that is not our intended result.

A demonstration of how the three frame conditions apply to an arbitrary solution is given in Figure 3.3. Here, we observe a pattern that we can directly describe the relation between the port X and Z, using a variable-sized frame condition. The frame conditions are given in Figure 3.4. These frame conditions apply for each row and are specified by:

$$\forall t. (Z(t) = * \land X(t) = * \lor (Z(t) = * \land \exists j.t < j \land X(j) = * \land Z(j) = X(t) \land \forall i.t < i \land i < j \rightarrow X(i) = * \land Z(i) = *) \lor (X(t) = * \land \exists j.j < t \land X(j) = Z(t) \land Z(j) = * \land \forall i.j < i \land i < t \rightarrow X(i) = * \land Z(i) = *) )$$

It means that for each row (at *t*), whenever *X* has value *d*, there must exists some future row (at *j*) such that *Z* has the same value *d*. The values at both ports that are intermediate between these two rows are required to be \*. It also means that for each row (at *t*), whenever *Z* has value *d*, there must exists a previous row with the same value, and all intermediate rows are required to be \*. Our frame condition is still sliding here: the condition that  $Z(t) = * \land X(t) = *$  is applied for all rows that are intermediate between the element accepted by *X* and then returned by *Z*.

We now turn to primitive components and composite components. The main point is to associate each primitive component to a coordination protocol. We then map composite components to coordination protocols, by induction on the construction of compositions.

**Definition 26.** A *component specification*  $\phi(U)$  consists of the following data:

$$\frac{X \ Z}{\underbrace{\ast \ \ast}} \quad \frac{X \ Z}{\underbrace{d \ \ast}}_{\underbrace{\ast \ \ast}} \quad \frac{d \ \ast}{\underbrace{d \ \ast}}_{\underbrace{\ast \ \ast}} \ ()$$

Figure 3.4: Alternative frame conditions that make up a BUFFER.

- an interface  $U = \langle X_1, \dots, X_n \mid Z_1, \dots, Z_k \rangle$ ,

- a coordination protocol  $\phi$ .

The free variables of the coordination protocol  $\phi$  are all ports assigned in solutions; the interface marks which ports are not hidden. Without loss of generality, we may assume that all free variables of  $\phi$  are precisely the ports occurring in *U*: all hidden variables are existentially quantified, and for a non-occurring port *Y* we add a trivial clause  $\forall t.Y(t) = Y(t)$ .

The semantics of a component specification is the semantics of the coordination protocol,  $\mathcal{L}(\phi) = \{\beta \mid \beta \vDash \phi\}$  where  $\beta$  are solutions that assign streams to the ports occurring in *U*. We use the notation  $\mathcal{L}(\phi(U))$  to indicate that  $\phi$  and thus  $\mathcal{L}(\phi)$  depend on *U*. We introduce two abbreviations, useful for writing formulas that are indexed over interfaces:

Given an interface  $U = \langle X_1 : \alpha_1, \ldots, X_n : \alpha_n | Z_1 : \alpha_{n+1}, \ldots, Z_k : \alpha_{n+k} \rangle$ . We write  $\forall \vec{Y} : U.\phi$  as an abbreviation for the indexed quantification  $\forall Y_1^{\alpha_1} . \forall Y_2^{\alpha_2} . \ldots \forall Y_{n+k}^{\alpha_{n+k}} . \phi$ . Here  $Y_i$  are the bound variables, that correspond for  $1 \le i \le n$  to the input ports and for  $n < i \le n + k$  to the output ports. A similar abbreviation is used for  $\exists \vec{Y} : U.\phi$ . In the case U is empty, then  $\forall \vec{Y} : U.\phi$  is  $\top$  and  $\forall \vec{Y} : U.\phi$  is  $\bot$ . Similarly, we write  $\bigvee_{i \in U} \phi$  for an indexed disjunction and  $\bigwedge_{i \in U}$  for an indexed conjunction. Given a component specification  $\phi(U)$  then by  $\phi(\vec{Y})$  within an indexed quantification, we mean the simultaneous substitution of the free variables  $X_1, \ldots, X_n, Z_1, \ldots, Z_k$  in  $\phi$  by those of  $\vec{Y}$ : namely the coordination protocol  $\phi[Y_1/X_1, \ldots, Y_n/X_n, Y_{n+1}/Z_1, \ldots, Y_{n+k}/Z_k]$ .